AMD baru saja menjelaskan lebih lanjut teknologi desain Chiplet Multi-Layer untuk prosesor mereka di masa depan. Mereka pun akan mengintegrasikan teknologi ini dengan prosesor dengan arsitektur Zen 3 mendatang dengan teknologi 3D V-Cache.

AMD menjelaskan lebih lanjut mengenai Multi-Layer yang akan menampilkan chip hybrid 2D/2.5D & 3D Chiplet Teknologi.

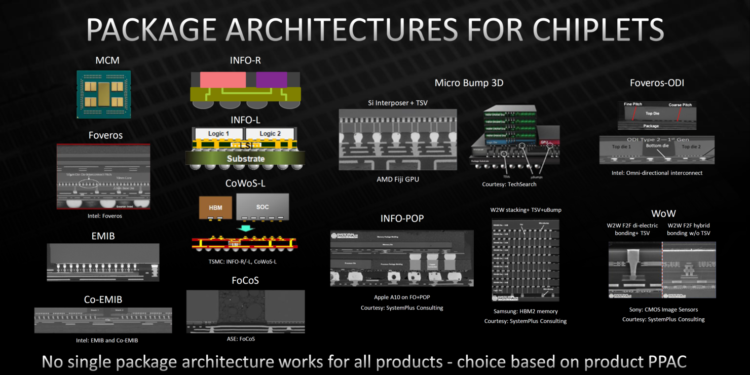

Mereka telah berbicara tentang desain chiplet yang sudah ada dan apa yang akan digunakan di masa depan dalam hal pengembangan chip multi-layer. Saat ini, ada 14 paket arsitektur untuk chiplet dalam pengembangan untuk berbagai produk baik itu yang sudah dirilis maupun yang akan dirilis.

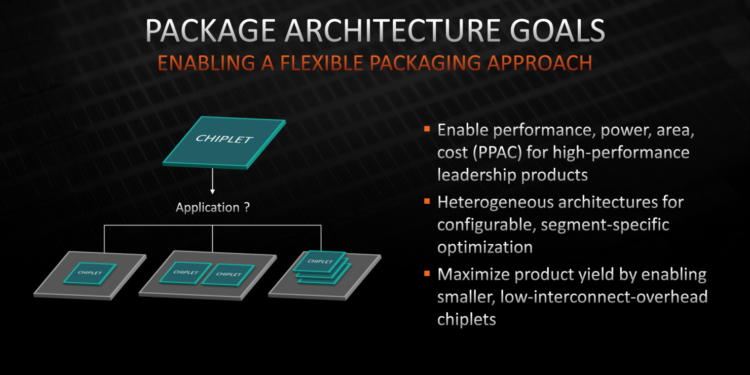

AMD mengatakan kalau pilihan packaging dan arsitektur chiplet tergantung pada kinerja, daya, area dan biaya produk masing-masing. Menurut AMD, 2021 akan menandai pengenalan pertama dari arsitektur Chiplet 3D.

Kita telah melihat teknologi 2D dan 2.5D pada produk konsumer dan server dengan 3D V-Cache, selanjutnya AMD akan masuk ke 3D chiplet dengan teknik stacking. Produk pertama yang akan menggunakan teknologi ini adalah AMD Zen 3 yang akan menampilkan cache SRAM diatas CCD Zen 3.

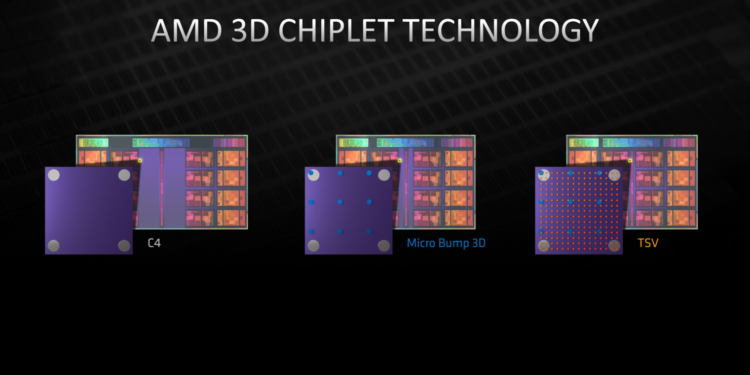

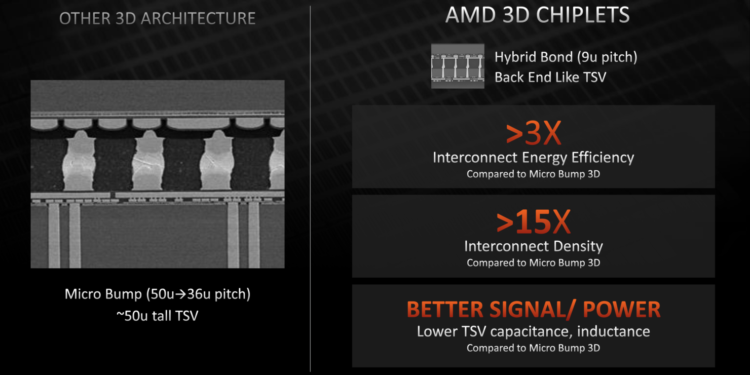

Penggunaan teknologi chiplet 3D juga meningkatkan interkoneksi pada prosesor. Beberapa gambaran untuk teknologi 3D Chiplet pada Zen 3 CCD ditampilkan disini :

Teknologi AMD terbukti menambah efisiensi dan performa

AMD telah membagikan bagaimana mengintegrasikan 3D V-Cache diatas CCD Zen 3. Hal ini dicapai melalui penggunaan Micro Bump (3D) dan beberapa interkoneksi seperti disebutkan diatas. Interkoneksi menggunakan ikatan-ikatan dielektrik hidrofilik baru dengan ikatan unit komputasi langsung yang dirancang dan dioptimalkan dengan TSMC.

Dua silikon individu (chiplet) terikat menjadi satu kesatuan menggunakan teknologi ini. Menurut AMD, ikatan hybrid memiliki pitch 9u dan back-end mirip dengan TSV yang sedikit lebih kecil dari interkoneksi Forveros Intel yang memiliki pitch 10u.

Efisiensi energi interkoneksi dinilai lebih tinggi 3x lipat dibandingkan dengan Micron Bump 3D, kepadatan interkoneksi pun juga dinilai 15x lebih tinggi. Chiplet 3D ini juga menawarkan sinyal/daya yang lebih baik berkat penurunan kapasitansi TSV dan induktansi.

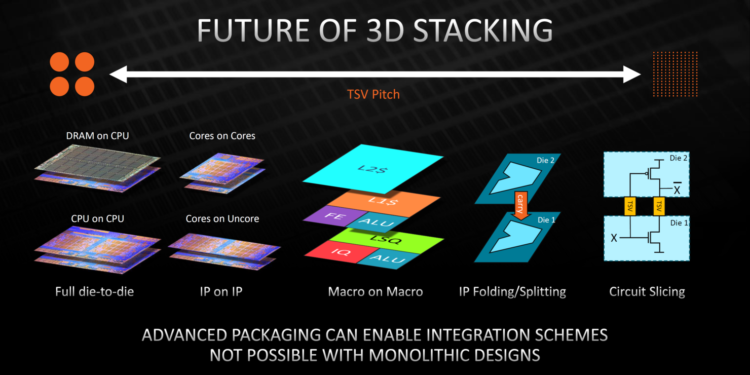

AMD juga menegaskan bahwa DRAM pada CPU hanyalah awal dari apa yang dapat mereka capai dari teknik 3D Stacking. Di masa depan, AMD berharap untuk memanfaatkan 3D stacking untuk menumpuk inti diatas inti, IP diatas IP dan segalanya bisa menjadi sangat liar ketika Macroblock dapat ditumpuk 3D diatas Makroblok lainnya.

via Pemmzchannel